数字IC设计中的重要考虑因素

我们都知道,最近关于芯片设计与制造的话题,依然占据着人们的茶前饭后时间,敌人的围追堵截,使我们丢弃幻想,奋起抗争。在我们的工作中或生活中,不论处于半导体行业的上游还是下游,对于芯片都无法避开,缺了它,我们寸步难行。

当你在家开着空调,从冰箱里拿出一瓶冰可乐,葛优躺拿着手机刷视频时,你希望视频流畅无卡顿。在这背后,是一群群芯片设计工程师、移动通信工程师、网络工程师、图像处理工程师、芯片开发/验证工程师、芯片制造工程师、芯片封装测试工程师......日以继夜奋斗的结果。

任何一款芯片的设计,都需要庞大的设计和验证团队进行密切合作共同完成。在芯片设计中,我们需要考虑众多因素。那么,我们的脑海里在想些什么呢?

芯片逻辑开发工程师的三重境界:心中有电路,脑中有时序,手中有代码。

如果我们在设计中使用同步设计或任何IP,或最终确定体系结构和微体系结构,那么我们需要制定各种策略。以下列出了其中一部分:

设计的功能性和兼容性

并行性、并发性和流水线策略

外部IO和高速接口

设计的面积和初始门数估计

速度和最高频率要求

功耗要求和使用低功耗设计

时钟网络和延迟

接口和IO延迟与建模策略

经过以上考虑,由经验丰富的技术人员组成的团队最终确定ASIC/ SOC 设计的架构和微架构。

为了便于理解架构和项目研发,我们需要考虑的一些设计因素,主要有以下几个方面。

01

时序参数

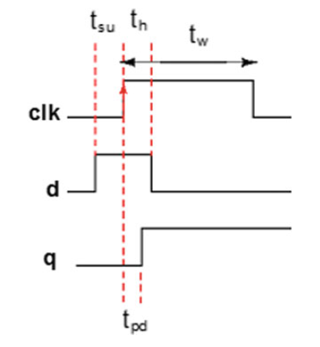

上升沿敏感触发器的重要时序参数如图1所示,它们是:

建立时间 (tsu)

保持时间(th)

触发传播延时(tpd)

图1 D触发器时序参数

建立时间(tsu):在时钟的有效边沿到达之前,触发器的数据输入应该保持稳定值的最小时间被称为建立时间。

有效边沿表示上升沿(正边沿)灵敏的D触发器从低电平到高电平的跳变,下降沿(负边沿)灵敏的D触发器从高电平到低电平的跳变。

在建立时间窗口期间,如果数据输入从1到0或反之,那么触发器输出将是亚稳态的,这表明存在建立违例。

保持时间(th):触发器的数据输入在时钟有效边沿到达后保持稳定的最小时间,称为保持时间。

有效边沿表示上升沿(正边沿)灵敏的D触发器从低到高的跳变,下降沿(负边沿)灵敏的D触发器从高到低的跳变。

在保持时间窗口期间,如果数据输入从1到0或反之,那么触发器输出将是亚稳态的,这表明存在保持违例。

触发器的传播时延(tpd=tcq):触发器到达时钟有效边沿后产生有效输出所需的时间,称为触发器的传播时延。

传播延迟也称为时钟到q端的延迟,也称为tcq。

快发智造

快发智造